# FPGA BASED CONTROLLER DESIGN FOR SWITCHING CONVERTERS AND PERFORMANCE ANALYSIS

A THESIS SUBMITTED IN PARTIAL FULFILLMENT FOR THE DEGREE OF

## **DOCTOR OF PHILOSOPHY**

IN THE FACULTY OF ENGINEERING

GOA UNIVERSITY

By

## Smt. Sonali Dattatraya Pandit

## **Research Centre**

## **Department of Electrical and Electronics Engineering**

## Goa College of Engineering, Farmagudi

Goa

DECEMBER 2022

# **Dedication**

This dissertation is dedicated to my husband, Dattatraya, who has been a source of strength, support and motivation throughout this research. I am truly blessed for having you in my life.

I also dedicate this dissertation to my dear parents and parents-in-law for their unconditional love, support and encouragement.

# **Thesis Approval**

This thesis entitled **"FPGA BASED CONTROLLER DESIGN FOR SWITCHING CON-VERTERS AND PERFORMANCE ANALYSIS"** by Smt. Sonali Dattatraya Pandit is approved for the degree of **Doctor of Philosophy in Electrical and Electronics Engineering.**

|   | Examiners:  |

|---|-------------|

| 1 |             |

| 2 |             |

| 3 |             |

|   | Supervisor: |

|   |             |

|   | Principal:  |

.....

Date:

Place:

# DECLARATION

I, Sonali Dattatraya Pandit, hereby declare that this thesis represents work which has been carried out by me and that it has not been submitted, either in part or full, to any other University or Institution for the award of any research degree.

Place: Farmagudi, Ponda Date: Sonali Dattatraya Pandit

# CERTIFICATE

I hereby certify that the work was carried out under my supervision and may be placed for evaluation.

Dr. Vinayak N. Shet Professor and Ex-Principal Electrical and Electronics Engineering Department Goa College of Engineering Farmagudi, Ponda, Goa

#### Acknowledgement

A dissertation is not the outcome of the efforts of entirely one person. There are many people who have contributed in its development. At this time, I take the opportunity to acknowledge those who have made an impact on my doctoral journey and accomplishment.

First and foremost, I thank God for always being with me and blessing me throughout my research work so that it could be completed successfully.

I would like to express my deep and sincere gratitude to my research guide Dr.Vinayak N. Shet, Professor, Electrical and Electronics Engineering Department, Goa College of Engineering, Farmagudi for giving me an opportunity to do research under his guidance. I am indebted to him for providing his knowledge, motivation and invaluable guidance throughout the research. His scientific approach, meticulous scrutiny, timely advice and help have helped me to accomplish this task.

I would like to thank Dr.A. B. Raju, Professor, K.L.E. Technological University, Department of Electrical and Electronics Engineering, Hubbali, for his guidance, help and advice as a Doctoral Research Committee(DRC) member. I thank Dr.Anant Naik, Professor, Electrical and Electronics Engineering Department, Goa College of Engineering, Farmagudi, for his help, timely advice and guidance as a DRC member. Their constant motivation and words of encouragement have helped me during my research.

I would like to thank Dr. Vivek Kamat, Director of Technical Education, for his motivation and support. I am grateful to him for granting me the necessary permissions and government approvals to undertake part time Ph.D in the institution.

I am thankful to the Principals of Goa College of Engineering during my research years, Dr.V. N. Shet, Dr.Krupashankara M. S.and Dr.R. B. Lohani for their support and permissions to pursue my research work.

I am grateful to Dr.Govind Kuncolienker, Professor and Head of Electrical Engineering Department, Goa College of Engineering, for his support.

I am thankful to Goa University for having started the Ph.D. program at Goa College of Engineering. A special mention of thanks to the University academic staff handling the Ph.D.section and library staff of Goa University for their support.

I am thankful to the staff of Academic department of Goa College of Engineering for their help and support.

I would like to thank all my departmental colleagues and staff for their constant help and

support. I also thank the departmental laboratory assistants, technical assistants and staff for the support provided during experimentation work.

I acknowledge the support, help and motivation received from my researcher friends from college. Special thanks to my researcher friends from department for being with me throughout my journey of research and extending their continuous support and help.

I am grateful to my sister for proof reading of the thesis and thank her for the help and support. I thank all my dear friends for their best wishes, support and motivation.

I would not have been able to achieve this work without a strong support system at home. Their motivation and inspiration has helped me to achieve this feat and I am indebted to them. My husband, Dattatraya has been a constant source of motivation and I thank him sincerely for believing in me, giving me confidence and helping me achieve this goal. He was instrumental in convincing me to pursue my Ph.D and has been a pillar of strength. He has managed the home front efficiently when I was busy with my work. I thank my son Ishan and daughter Shravni for their love, cooperation and support, ensuring that I get quality time to complete my work. I thank my parents and parents-in-law for constantly supporting me, inspiring me and boosting my morale. I also thank my extended family and relatives for their constant encouragement and support.

#### SONALI PANDIT

#### Abstract

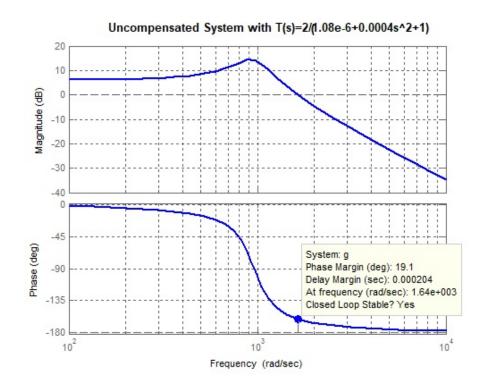

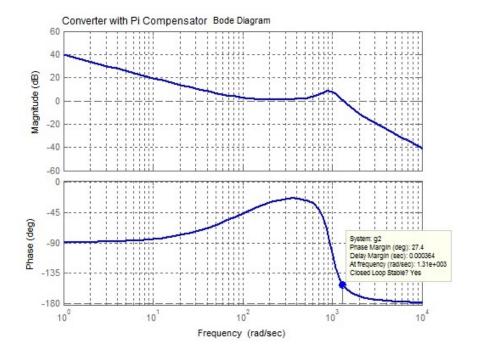

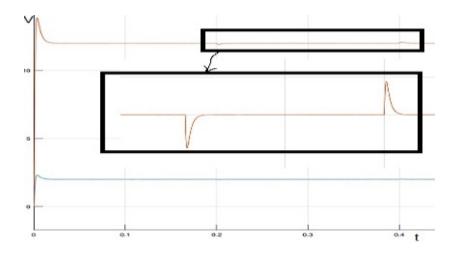

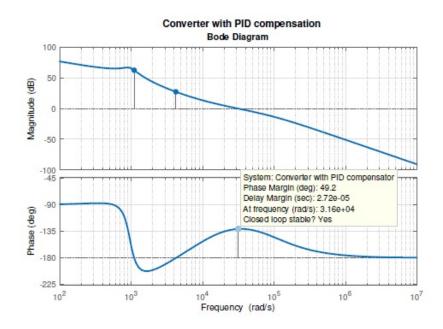

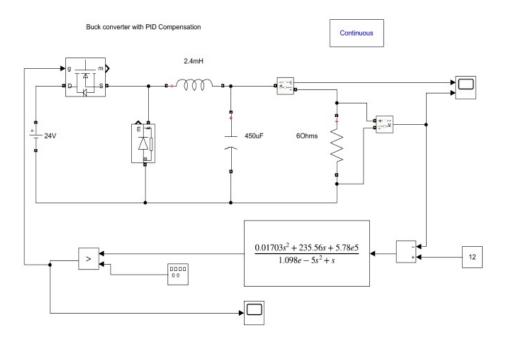

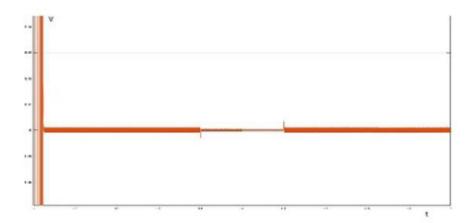

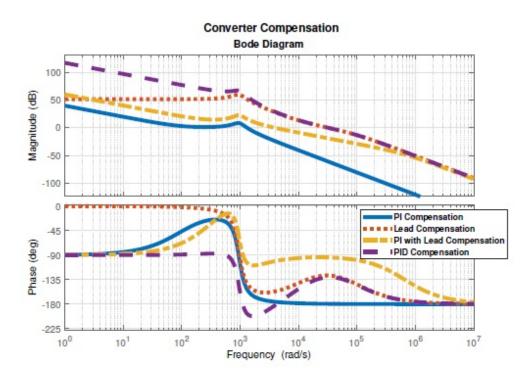

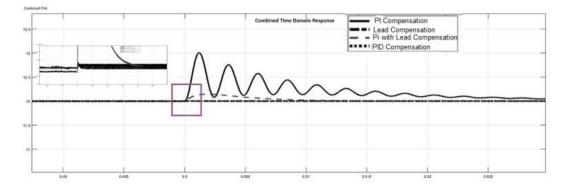

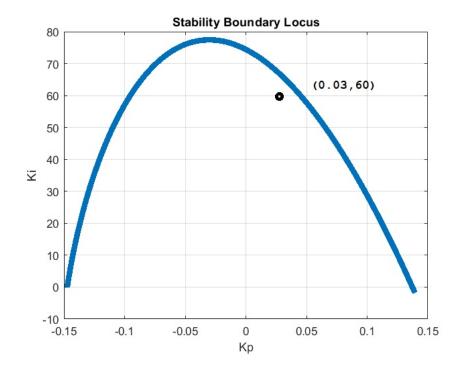

Electronic devices like cell phones, laptops require multiple dc supplies for charging and connecting various components like LCD display, USB devices. The AC-DC and DC-DC converters find a variety of applications in modern gadgets. They are also used in motor drives and power control. These switch mode converters employ a controller in the feedback loop to regulate the dc output voltage. A variety of controllers, both analog and digital, are used with different control techniques. The controllers designed are of various technologies like analog, microcontroller, neural network, fuzzy logic, DSP and VLSI etc. VLSI system design has the better advantages of high speed, small area, low cost, reliability and reprogrammability. In this research, design and implementation of a controller for switching converters using the FPGA based design and VLSI technology is proposed. Buck and boost converters were designed and analyzed using the state space averaging method. Simulations were performed using Matlab Simulink for an open loop and closed loop control. Different types of compensators viz, PI, Lead, Lead with PI and PID were designed and simulated in Simulink environment for these converters. Comparison of all these proposed compensators in time and frequency domain is analyzed. Compared to the uncompensated converter, PI controller so designed improves the phase margin from 19.1° to 27.4°. The gain cross over frequency is also increased to 1.31 krad/s from 960 rad/s. Using a PID controller, the phase margin obtained is  $49.2^{\circ}$ , its overshoot is 0.03% and a settling time of 1.5 msec.

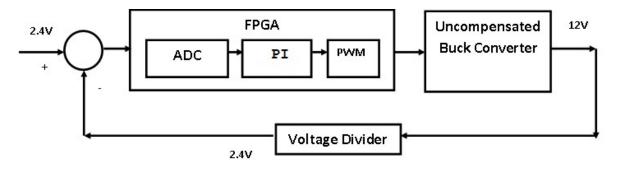

PI and PID controllers were designed using the platform of VHDL language. Finite state machine modeling is adapted to implement the said controllers. The control loop consisting of a digital comparator, digital controller and the pulse width modulator is implemented on Spartan 3M FPGA. An onboard analog to digital converter (ADC) is interfaced using VHDL. Xilinx 14.1 Project Navigator is used to simulate and synthesize the control loop. Functional simulation is performed using ISim simulator. Logic analyser Chipscope, which is implemented in the FPGA is used to obtain the PWM output in real time. The buck and boost converters were implemented on hardware and interfaced with the proposed PI and PID controllers. Performance of the converters is tested with open loop and closed loop configurations for varying input voltage and varying load currents. An optimum controller is proposed using the design aspects of finite state modeling. Voltage regulation is improved using a PI and a PID controller. The finite state machine modeling of a PID controller has a reduced hardware of 112 slice flipflops and 60 LUT's as compared to a multiplier based

controller.

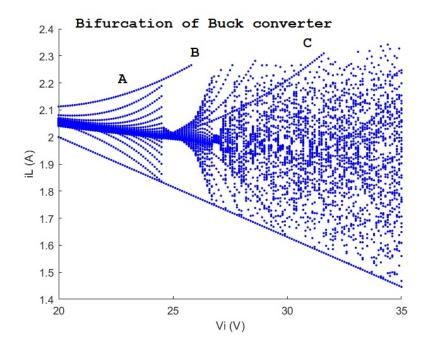

The switching devices in the converter and the associated passive components in the switching converters will give rise to non-linearity. The buck and boost converters are analyzed for the non linearity. The discrete iterative maps for the converters were derived. The discrete maps were simulated in Matlab environment for variations in input voltage and reference current to obtain the bifurcation diagrams. The output of the converters is obtained for the input voltage in the period 1, period 2 and chaos regions using Matlab Simulink. Non linearity regions of the converters were observed wherein the switching converters exhibit chaotic behavior of operation.

# Contents

| 1 | Intr | oduction                                             | 1  |

|---|------|------------------------------------------------------|----|

|   | 1.1  | Types of DC-DC converters                            | 1  |

|   |      | 1.1.1 Performance Evaluation of Switching Converters | 3  |

|   |      | 1.1.2 Necessity of Controller                        | 5  |

|   |      | 1.1.3 Non linear Characteristics                     | 6  |

|   |      | 1.1.4 VLSI Design Technology-FPGA Platform           | 6  |

|   | 1.2  | Organization of the Report                           | 7  |

| 2 | Lite | rature Review                                        | 9  |

|   | 2.1  | Switching Converters                                 | 9  |

|   | 2.2  | Digital Control methods                              | 10 |

|   | 2.3  | FPGA based control                                   | 13 |

|   | 2.4  | FPGA based discrete controllers                      | 16 |

|   | 2.5  | Non Linear performance of switching converters       | 17 |

|   | 2.6  | Research gap and objectives                          | 22 |

|   | 2.7  | Conclusion                                           | 23 |

| 3 | Buc  | ck converter with proposed Controller                | 24 |

|   | 3.1  | Introduction                                         | 24 |

|   | 3.2  | Buck converter working principle                     | 24 |

|   | 3.3  | Modeling of a Buck converter                         | 28 |

|   | 3.4  | Buck converter Design                                | 32 |

|   | 3.5  | Compensation for a Buck converter                    | 34 |

|   |      | 3.5.1 Proportional Integral (PI) Compensator         | 38 |

|   |      | 3.5.2 Lead Compensator                               | 40 |

|   |      | 3.5.3 Combined PI and Lead Compensator                     | 42       |

|---|------|------------------------------------------------------------|----------|

|   |      | 3.5.4 PID Compensator                                      | 45       |

|   |      | 3.5.5 Results                                              | 47       |

|   | 3.6  | PI Controller design using stability boundary locus method | 49       |

|   | 3.7  | Component selection for buck converter                     | 53       |

|   | 3.8  | Hardware Implementation of a buck converter                | 55       |

|   | 3.9  | Performance Evaluation of buck converter                   | 56       |

|   |      | 3.9.1 Open Loop Configuration                              | 57       |

|   |      | 3.9.2 Closed Loop Configuration                            | 62       |

|   | 3.10 | Conclusion                                                 | 67       |

|   |      |                                                            |          |

| 4 |      |                                                            | 68       |

|   | 4.1  |                                                            | 68       |

|   | 4.2  |                                                            | 68       |

|   | 4.3  | 1 2                                                        | 70       |

|   | 4.4  | 6                                                          | 73       |

|   | 4.5  | Boost converter simulation                                 | 73       |

|   | 4.6  | Boost converter component selection                        | 75       |

|   | 4.7  | Hardware implementation                                    | 76       |

|   | 4.8  | Performance Evaluation                                     | 77       |

|   |      | 4.8.1 Open Loop Configuration                              | 77       |

|   |      | 4.8.2 Closed Loop Configuration                            | 84       |

|   | 4.9  | Conclusion                                                 | 88       |

| 5 | FPG  | A based Controller Design                                  | 89       |

| J | 5.1  |                                                            | 89       |

|   | 5.2  |                                                            | 89       |

|   | 5.3  |                                                            | 91       |

|   | 5.4  | 6                                                          | 92       |

|   | 5.4  |                                                            | 92<br>93 |

|   |      |                                                            | 93<br>93 |

|   |      | 1                                                          | 93<br>94 |

|   | 5 5  |                                                            | 94<br>94 |

|   | 5.5  | Digital PI Controller                                      | 74       |

|    |                  | 5.5.1 Behavioral modeling                       | 95  |

|----|------------------|-------------------------------------------------|-----|

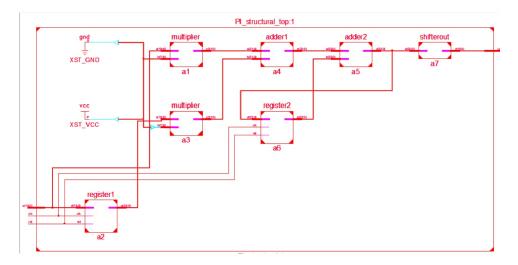

|    |                  | 5.5.2 Structural modeling                       | 95  |

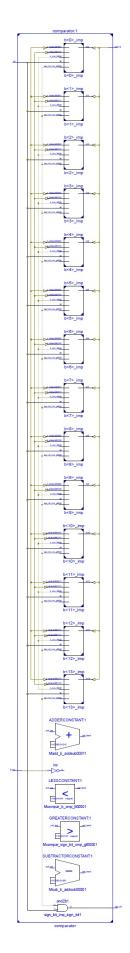

|    |                  | 5.5.3 Finite State Machine based modeling       | 96  |

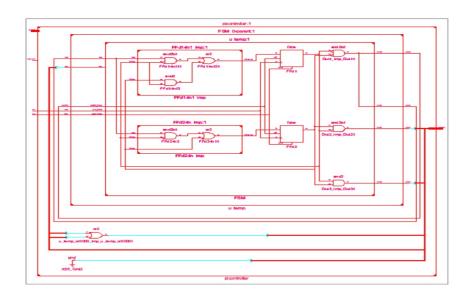

|    | 5.6              | Hardware of the control loop                    | 98  |

|    | 5.7              | Simulation                                      | 105 |

|    | 5.8              | PID Controller                                  | 106 |

|    | 5.9              | Conclusion                                      | 110 |

| 6  | Cha              | os and Bifurcation Analysis                     | 111 |

|    | 6.1              | Introduction                                    | 111 |

|    | 6.2              | Bifurcation and Chaos                           | 111 |

|    | 6.3              | Analysis of Buck converter                      | 112 |

|    |                  | 6.3.1 Discrete iterative map of buck converter  | 113 |

|    |                  | 6.3.2 Simulations for buck converter            | 114 |

|    | 6.4              | Analysis of boost converter                     | 117 |

|    |                  | 6.4.1 Discrete iterative map of boost converter | 117 |

|    |                  | 6.4.2 Simulations for boost converter           | 119 |

|    | 6.5              | Conclusion                                      | 125 |

| 7  | Con              | clusions and Future work                        | 126 |

|    | 7.1              | Conclusion                                      | 126 |

|    | 7.2              | Future work                                     | 127 |

| Re | eferen           | ices                                            | 128 |

| Ρı | Publications 135 |                                                 |     |

# **List of Tables**

| 3.1                                                                                                                 | Buck Converter Parameters                                                                                                                                                                                                                                                                                                        | 33                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 3.2                                                                                                                 | Frequency Domain Analysis for buck converter                                                                                                                                                                                                                                                                                     | 47                                                                                                         |

| 3.3                                                                                                                 | Time Domain Analysis for buck converter                                                                                                                                                                                                                                                                                          | 49                                                                                                         |

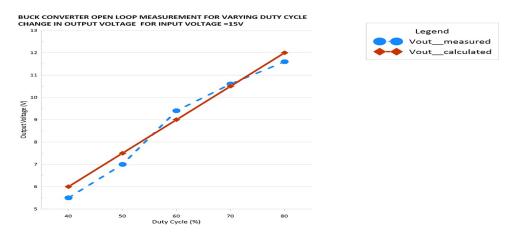

| 3.4                                                                                                                 | Open Loop varying duty cycle 24V input                                                                                                                                                                                                                                                                                           | 57                                                                                                         |

| 3.5                                                                                                                 | Open Loop varying duty cycle 18V input                                                                                                                                                                                                                                                                                           | 58                                                                                                         |

| 3.6                                                                                                                 | Open Loop varying duty cycle 15V input                                                                                                                                                                                                                                                                                           | 58                                                                                                         |

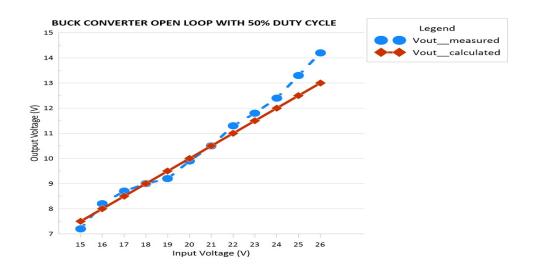

| 3.7                                                                                                                 | Open Loop varying input Voltage for 50%Duty Cycle                                                                                                                                                                                                                                                                                | 60                                                                                                         |

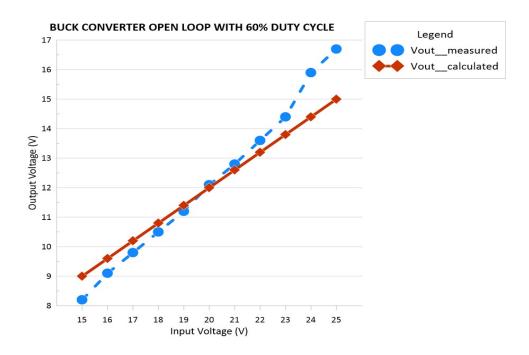

| 3.8                                                                                                                 | Open Loop varying input Voltage for 60%Duty Cycle                                                                                                                                                                                                                                                                                | 61                                                                                                         |

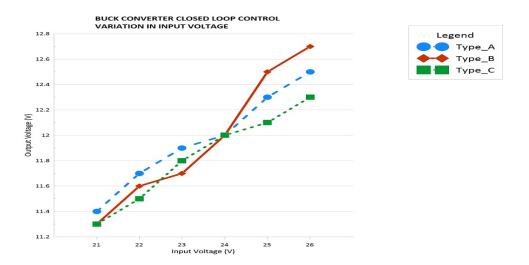

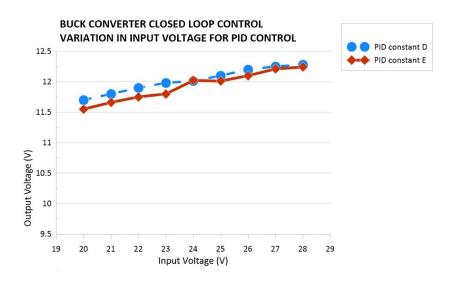

| 3.9                                                                                                                 | Closed Loop buck Converter output voltage for varying input voltage                                                                                                                                                                                                                                                              | 62                                                                                                         |

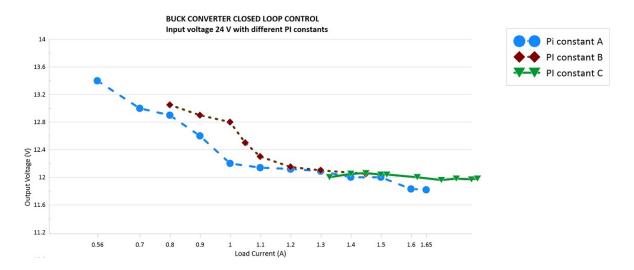

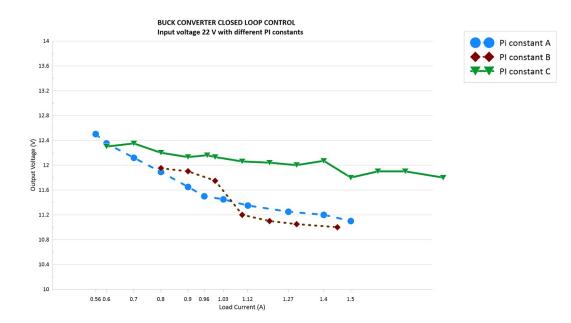

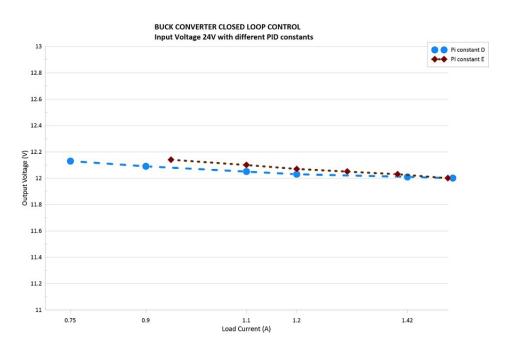

| 3.10                                                                                                                | Closed Loop varying Load Current for input voltage 24V                                                                                                                                                                                                                                                                           | 63                                                                                                         |

| 3.11                                                                                                                | Closed Loop varying Load Current for input voltage 22V                                                                                                                                                                                                                                                                           | 64                                                                                                         |

| 3.12                                                                                                                | Performance Evaluation for Buck converter using PI controller                                                                                                                                                                                                                                                                    | 65                                                                                                         |

| 3.13                                                                                                                | Performance Evaluation for Buck converter using PID controller                                                                                                                                                                                                                                                                   | 66                                                                                                         |

| 4.1                                                                                                                 | Boost Converter Parameters                                                                                                                                                                                                                                                                                                       | 73                                                                                                         |

|                                                                                                                     |                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                         |

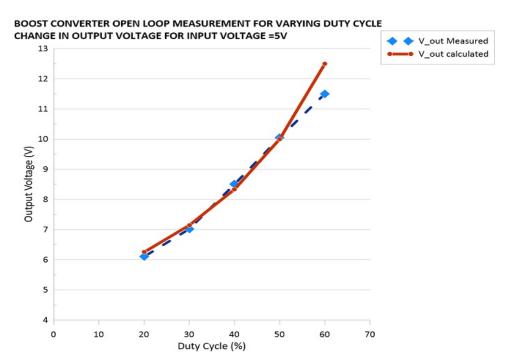

| 4.2                                                                                                                 | Boost Converter Open Loop varying duty cycle 5V input                                                                                                                                                                                                                                                                            | 78                                                                                                         |

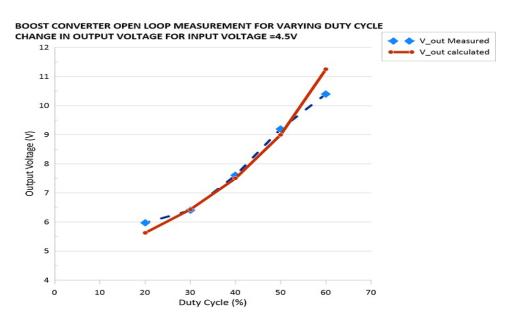

| 4.2<br>4.3                                                                                                          |                                                                                                                                                                                                                                                                                                                                  |                                                                                                            |

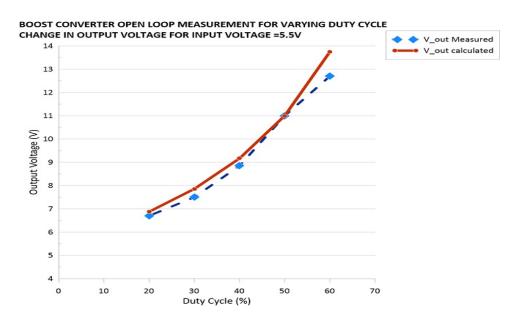

|                                                                                                                     | Boost Converter Open Loop varying duty cycle 5V input                                                                                                                                                                                                                                                                            | 78                                                                                                         |

| 4.3                                                                                                                 | Boost Converter Open Loop varying duty cycle 5V input                                                                                                                                                                                                                                                                            | 78<br>78                                                                                                   |

| 4.3<br>4.4                                                                                                          | Boost Converter Open Loop varying duty cycle 5V input                                                                                                                                                                                                                                                                            | 78<br>78<br>79                                                                                             |

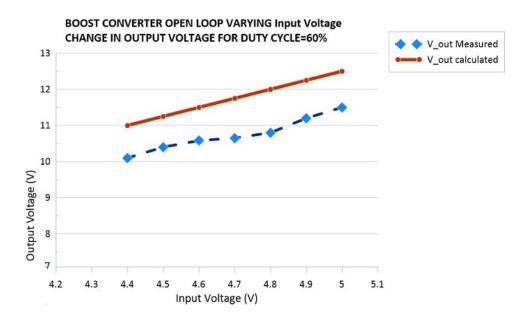

| <ul><li>4.3</li><li>4.4</li><li>4.5</li></ul>                                                                       | Boost Converter Open Loop varying duty cycle 5V input       .       .         Boost Converter Open Loop varying duty cycle 4.5V input       .       .         Boost Converter Open Loop varying duty cycle 5.5V input       .       .         Boost Converter Open Loop varying input Voltage for 60% Duty Cycle       .       . | 78<br>78<br>79<br>81                                                                                       |

| <ul><li>4.3</li><li>4.4</li><li>4.5</li><li>4.6</li></ul>                                                           | Boost Converter Open Loop varying duty cycle 5V input                                                                                                                                                                                                                                                                            | 78<br>78<br>79<br>81<br>82                                                                                 |

| <ol> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ol>                                         | Boost Converter Open Loop varying duty cycle 5V input                                                                                                                                                                                                                                                                            | <ol> <li>78</li> <li>78</li> <li>79</li> <li>81</li> <li>82</li> <li>83</li> </ol>                         |

| <ul> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> </ul>               | Boost Converter Open Loop varying duty cycle 5V input                                                                                                                                                                                                                                                                            | <ul> <li>78</li> <li>78</li> <li>79</li> <li>81</li> <li>82</li> <li>83</li> <li>84</li> </ul>             |

| <ul> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> <li>4.10</li> </ul> | Boost Converter Open Loop varying duty cycle 5V input                                                                                                                                                                                                                                                                            | <ol> <li>78</li> <li>78</li> <li>79</li> <li>81</li> <li>82</li> <li>83</li> <li>84</li> <li>85</li> </ol> |

| 5.1 | FSM sequence                                                   | 97  |

|-----|----------------------------------------------------------------|-----|

| 5.2 | Device utilization for PI controller using behavioral modeling | 100 |

| 5.3 | Device utilization for PI controller using structural modeling | 103 |

| 5.4 | Device utilization for PI controller using FSM                 | 104 |

| 5.5 | FSM sequence for PID controller                                | 108 |

| 5.6 | Device utilization for PI controller FSM                       | 110 |

# **List of Figures**

| 1.1  | Basic types of converter                                               | 4  |

|------|------------------------------------------------------------------------|----|

| 1.2  | Pulse Width Modulation                                                 | 6  |

| 1.3  | Programmable Logic devices                                             | 7  |

| 2.1  | Parallel architecture of Discrete PID for FPGA design [38]             | 17 |

| 2.2  | Phase portraits of (a) period-1, (b) period-2, and (c) chaos. [47]     | 18 |

| 2.3  | Bifurcation diagram of boost converter [47]                            | 19 |

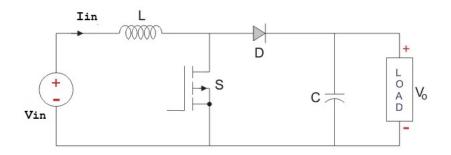

| 3.1  | Buck converter                                                         | 25 |

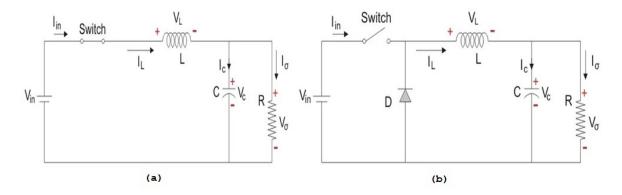

| 3.2  | Buck Converter working (a) Mode 1:switch closed (b) Mode 2:switch open | 25 |

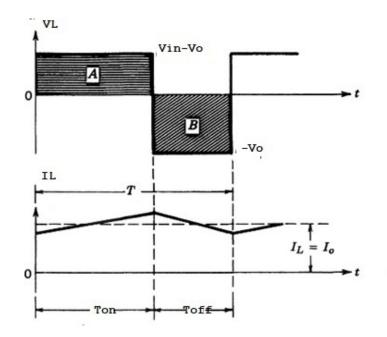

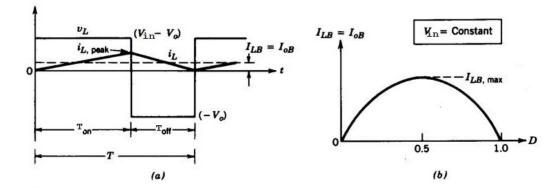

| 3.3  | Voltage current characteristics of buck converter                      | 27 |

| 3.4  | Boundary conditions of inductor current                                | 27 |

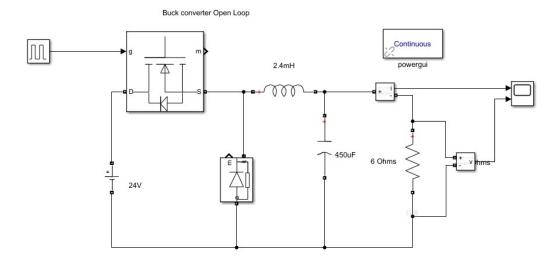

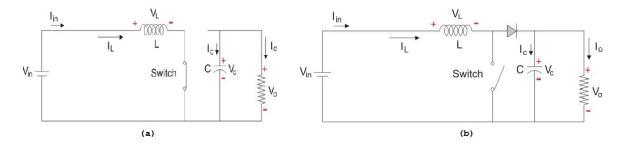

| 3.5  | Open Loop Buck converter model                                         | 33 |

| 3.6  | Open Loop Buck converter Simulation                                    | 34 |

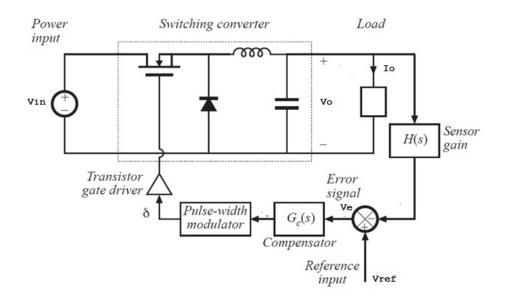

| 3.7  | Buck Converter closed loop configuration[1]                            | 35 |

| 3.8  | Bode Plot for uncompensated buck converter                             | 36 |

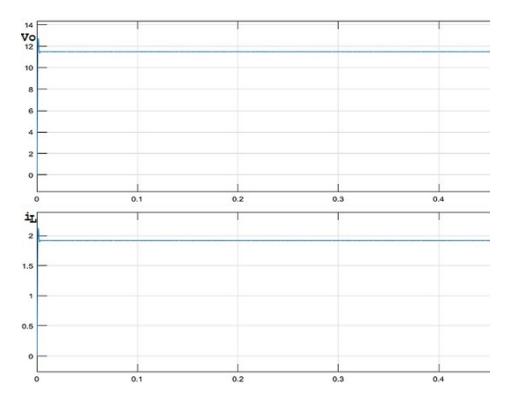

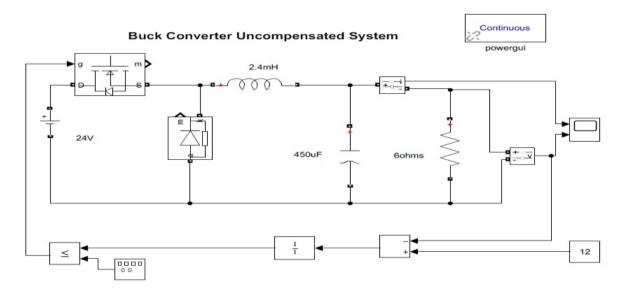

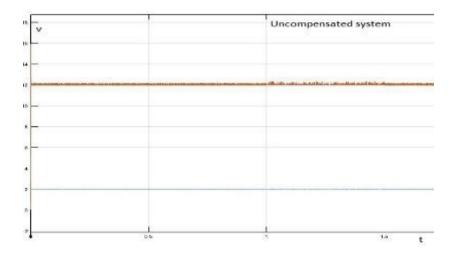

| 3.9  | Matlab Simulation of an Uncompensated system                           | 37 |

| 3.10 | Uncompensated simulink waveform                                        | 37 |

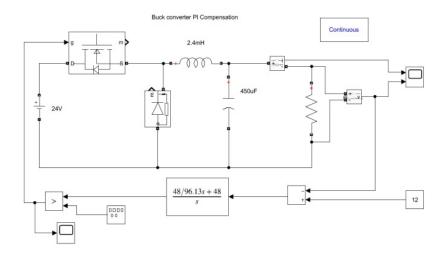

| 3.11 | Bode plot of buck converter with PI compensation                       | 39 |

| 3.12 | Buck Converter model with PI compensation                              | 40 |

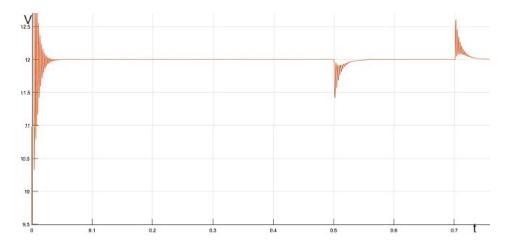

| 3.13 | Buck Converter output for PI compensation                              | 40 |

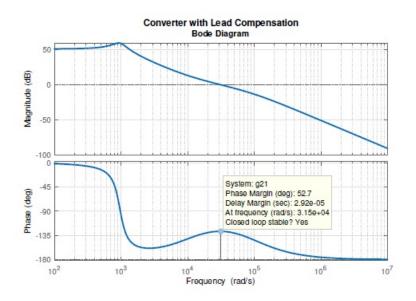

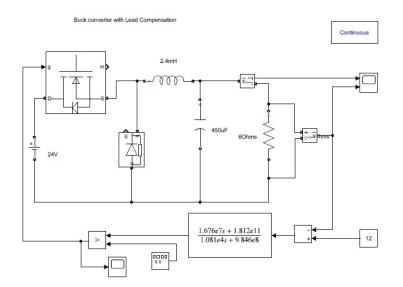

| 3.14 | Bode plot of buck converter with lead compensation                     | 41 |

| 3.15 | Buck Converter with Lead compensation model                            | 42 |

| 3.16 | Buck Converter Output with Lead compensation model                     | 42 |

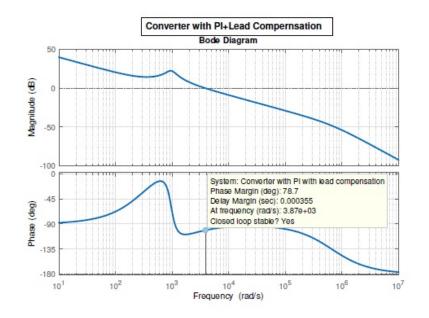

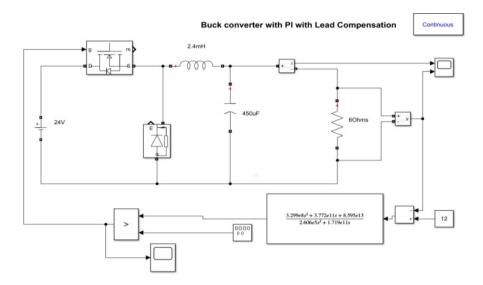

| 3.17 | Bode plot of buck converter with PI and Lead compensation              | 43 |

| 3.18 | Buck Converter with PI and lead compensation model                     | 44 |

| 3.19 | Buck Converter Output with PI with lead compensator                            | 44 |

|------|--------------------------------------------------------------------------------|----|

| 3.20 | Bode plot of buck converter with PID compensation                              | 46 |

| 3.21 | Buck Converter PID compensation model                                          | 46 |

| 3.22 | Buck Converter Output with PID compensator                                     | 47 |

| 3.23 | Combined Bode Plot for buck converter with the compensators                    | 48 |

| 3.24 | Combined time domain response of buck converter with the compensators .        | 48 |

| 3.25 | Implementation of the system                                                   | 50 |

| 3.26 | Stability Boundary Locus                                                       | 51 |

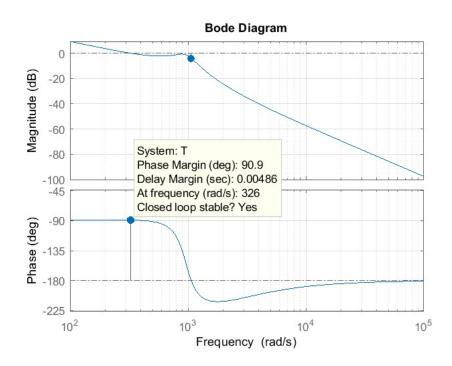

| 3.27 | Frequency Response of Compensated Buck Converter using Stability bound-        |    |

|      | ary locus                                                                      | 52 |

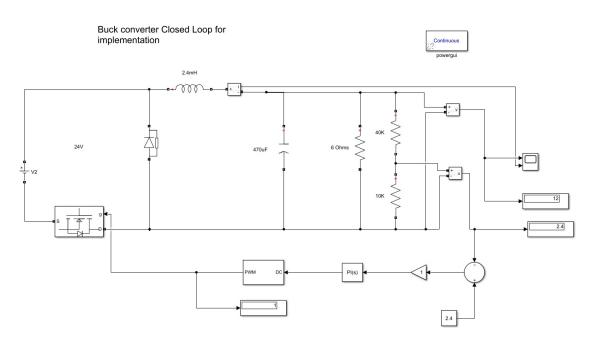

| 3.28 | Closed loop Buck Converter Model with tuned PI values                          | 52 |

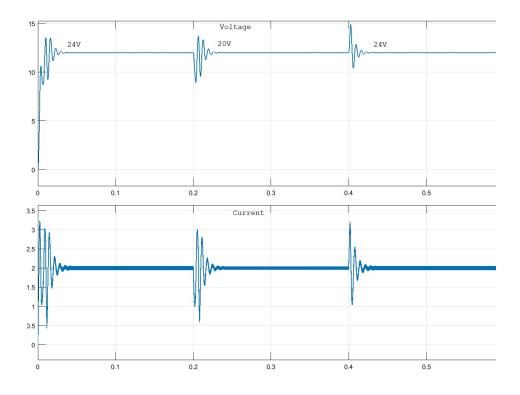

| 3.29 | Closed loop Buck Converter Simulation with tuned PI values                     | 53 |

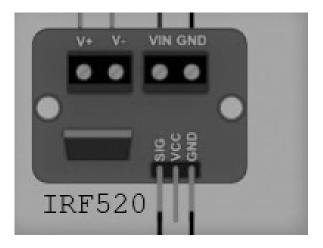

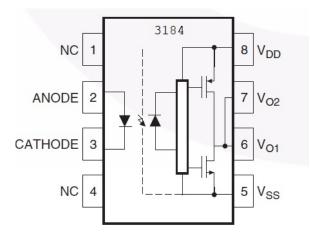

| 3.30 | MOSFET IRF520 Board                                                            | 54 |

| 3.31 | Mosfet driver                                                                  | 55 |

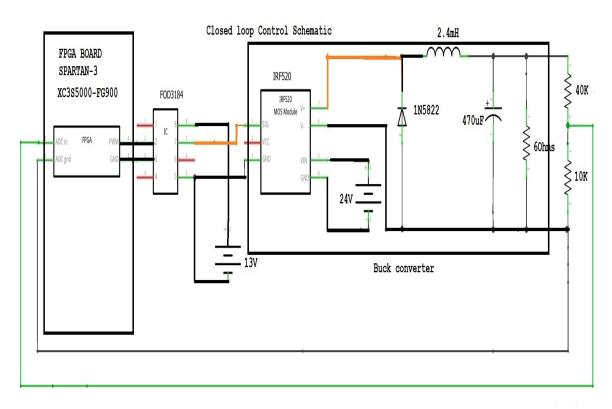

| 3.32 | Hardware implementation schematic for a buck converter                         | 56 |

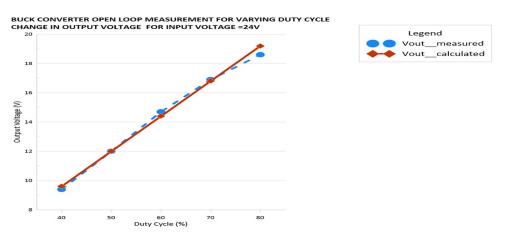

| 3.33 | Buck Open loop measurement Vin=24V                                             | 58 |

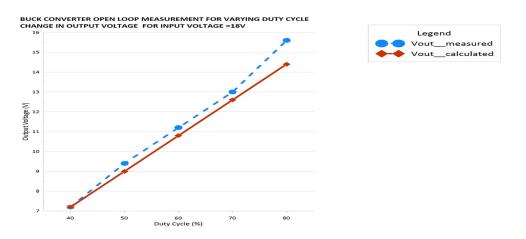

| 3.34 | Buck Open loop measurement Vin=18V                                             | 59 |

| 3.35 | Buck Open loop measurement Vin=15V                                             | 59 |

| 3.36 | Buck Open loop measurement Duty Cycle=50%                                      | 60 |

| 3.37 | Buck Open loop measurement Duty Cycle=60%                                      | 61 |

| 3.38 | Buck Converter Closed loop variation in input voltage                          | 63 |

| 3.39 | Buck Converter Closed loop output voltage variation for 24V input              | 64 |

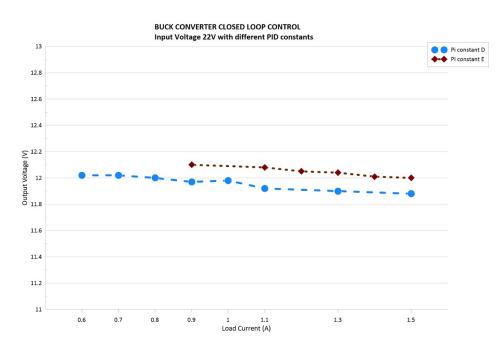

| 3.40 | Buck Converter Closed loop output voltage variation for 22V input              | 65 |

| 3.41 | Buck Converter with PID control for variation in input voltage                 | 66 |

| 3.42 | Buck Converter with PID control for changes in load with input voltage 24V     | 66 |

| 3.43 | Buck Converter with PID control for changes in load with input voltage 22V     | 67 |

| 4.1  | Boost converter                                                                | 69 |

| 4.2  | Boost converter working (a) Mode 1: switch closed (b) Mode2:switch open        | 69 |

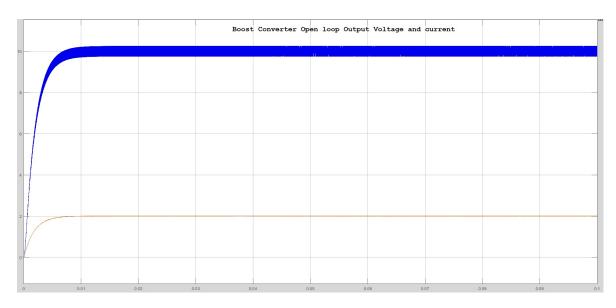

| 4.3  | Open loop simulation of the boost converter                                    | 74 |

| 4.4  | Output voltage and current for open loop boost converter Simulation            | 74 |

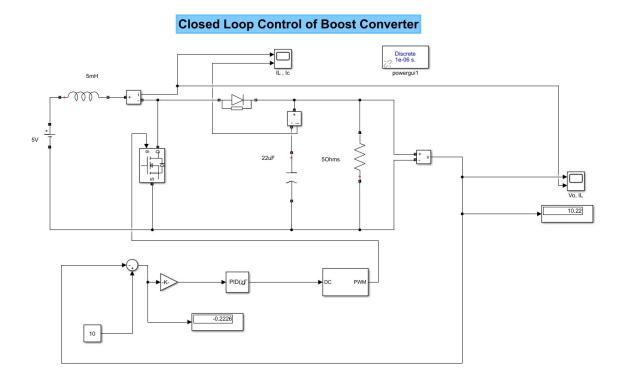

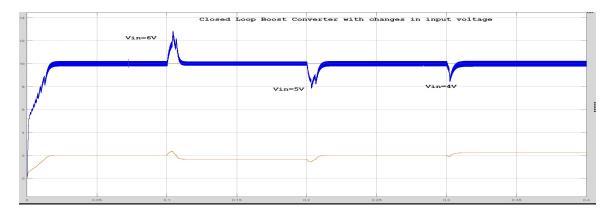

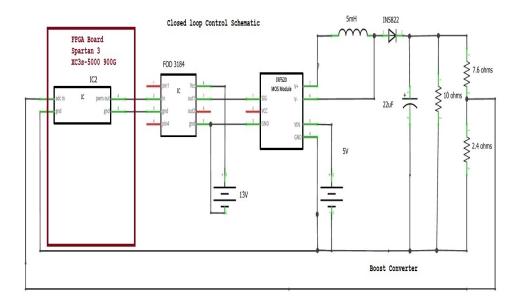

| 4.5  | Closed loop simulation of the boost converter                                  | 75 |

| 4.6  | Output Voltage and current for changes in the input voltage of Boost Converter | 75 |

| 4.7  | Hardware Implementation of the boost converter                             | 77  |

|------|----------------------------------------------------------------------------|-----|

| 4.8  | Boost Converter Open loop measurement Vin=5V                               | 79  |

| 4.9  | Boost Converter Open loop measurement Vin=4.5V                             | 80  |

| 4.10 | Boost Converter Open loop measurement Vin=5.5V                             | 80  |

| 4.11 | Boost Converter Open loop measurement Duty Cycle=60%                       | 81  |

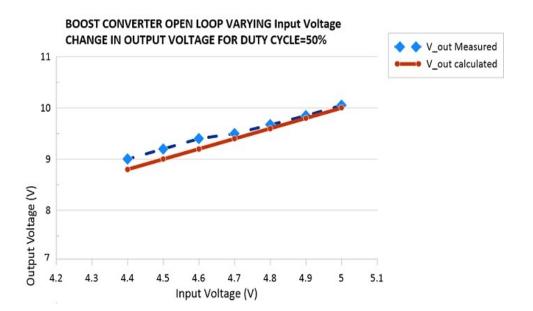

| 4.12 | Boost Converter Open loop measurement Duty Cycle=50%                       | 82  |

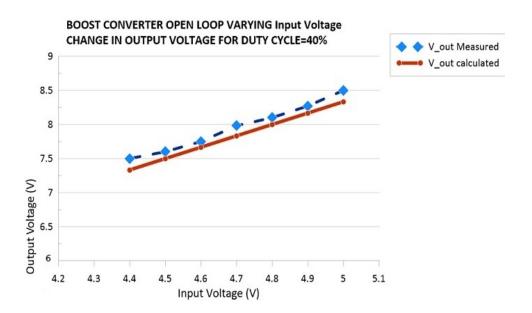

| 4.13 | Boost Converter Open loop measurement Duty Cycle=40%                       | 83  |

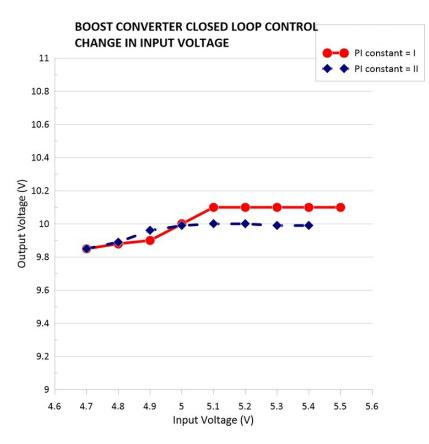

| 4.14 | Boost Converter Closed loop variation in input voltage                     | 85  |

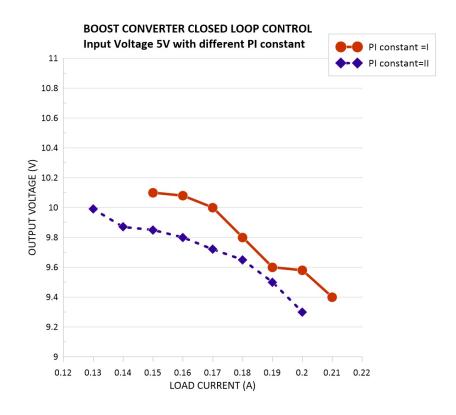

| 4.15 | Boost Converter Variation in output voltage with change in load-Vin=5V     | 87  |

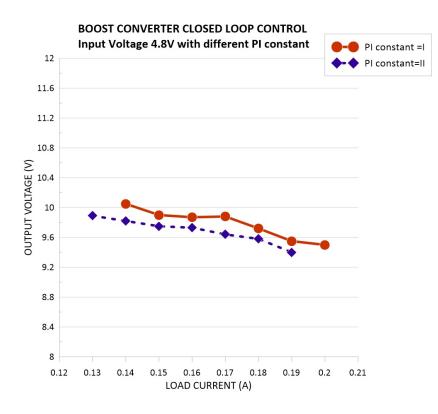

| 4.16 | Boost Converter Variation in output voltage with change in load-Vin=4.8V . | 87  |

| 5.1  | Structure of FPGA                                                          | 90  |

| 5.2  | Logic block of a FPGA                                                      | 90  |

| 5.3  | VLSI Design Flow                                                           | 91  |

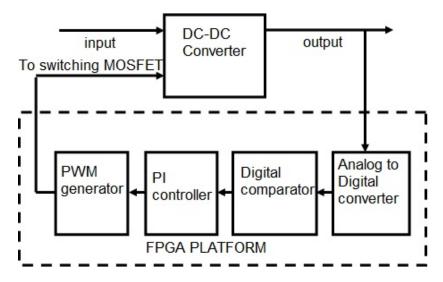

| 5.4  | Methodology for the feedback loop on FPGA                                  | 92  |

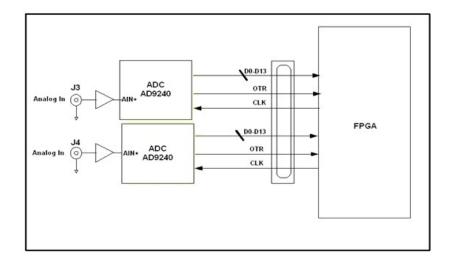

| 5.5  | ADC interfacing with the FPGA                                              | 93  |

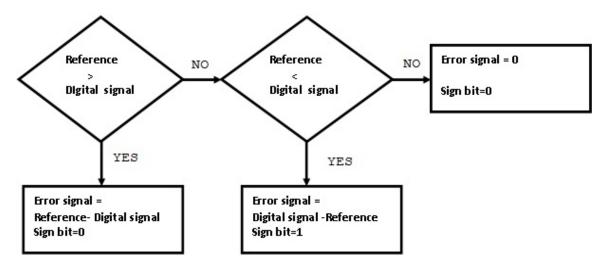

| 5.6  | Comparator Algorithm                                                       | 94  |

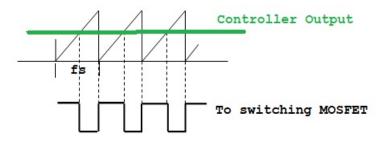

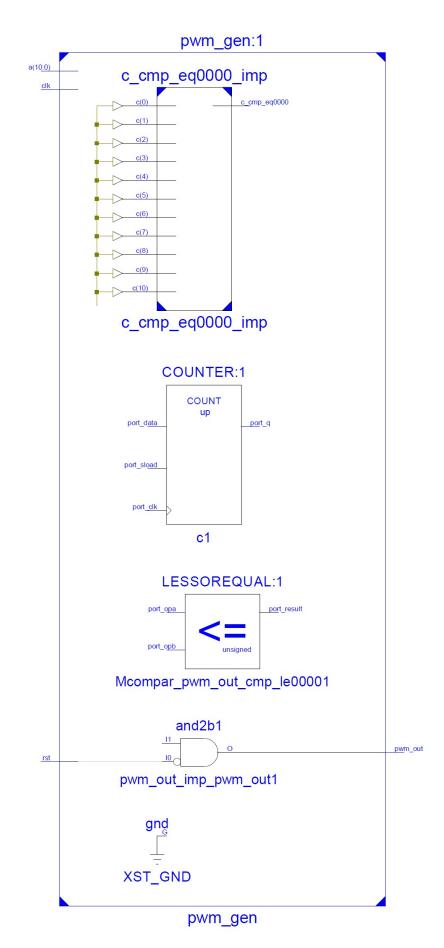

| 5.7  | Pulse width modulator                                                      | 94  |

| 5.8  | PI parallel structure                                                      | 96  |

| 5.9  | Finite State Machine for PI controller                                     | 97  |

| 5.10 | Block diagram of PI controller                                             | 98  |

| 5.11 | Synthesis of the feedback loop on FPGA                                     | 99  |

| 5.12 | Synthesis of ADC block                                                     | 99  |

| 5.13 | Synthesis of Comparator block                                              | 101 |

| 5.14 | Synthesis of PWM block                                                     | 102 |

| 5.15 | PI Behavioral Synthesis                                                    | 103 |

| 5.16 | PI Structural Synthesis                                                    | 103 |

| 5.17 | PI FSM Synthesis                                                           | 104 |

| 5.18 | Feedback loop Simulation                                                   | 105 |

| 5.19 | Real Time Simulation on Chipscope Logic analyzer for ADC input 1.9 V $$ .  | 106 |

| 5.20 | Real Time Simulation on Chipscope Logic analyzer for ADC input 2.9 V $$ .  | 106 |

| 5.21 | Finite state machine for PID controller                                    | 107 |

| 5.22 | Block diagram of PID controller                                            | 108 |

| 5.23 | PID FSM Synthesis                                                                      | 109 |

|------|----------------------------------------------------------------------------------------|-----|

| 5.24 | Feedback loop Simulation with PID controller                                           | 109 |

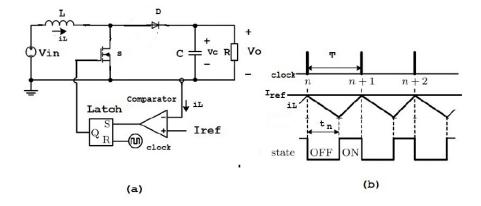

| 6.1  | Current controlled buck converter (a)Schematic (b)waveforms                            | 113 |

| 6.2  | Bifurcation diagram for Buck converter for $i_L$ with $V_{in}$ as a control parameter  |     |

|      | $(I_{ref}=2A)$                                                                         | 115 |

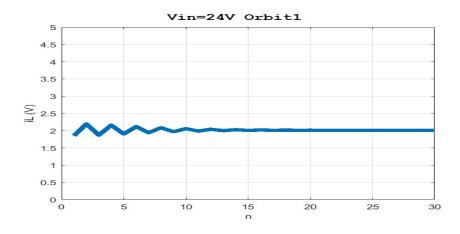

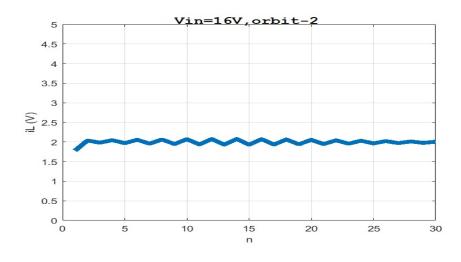

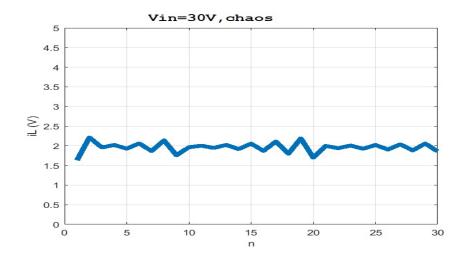

| 6.3  | Inductor current for Vin=24V                                                           | 116 |

| 6.4  | Inductor current for Vin=26V                                                           | 116 |

| 6.5  | Inductor current for Vin=30V                                                           | 116 |

| 6.6  | Current controlled boost converter (a)Schematic (b)waveforms                           | 117 |

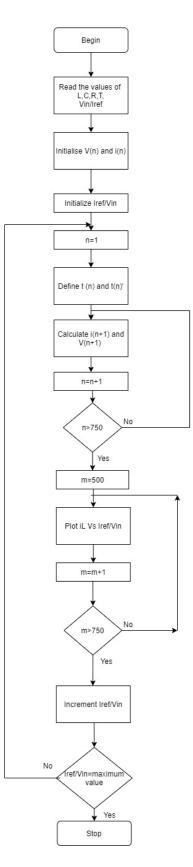

| 6.7  | Flowchart for bifurcation                                                              | 120 |

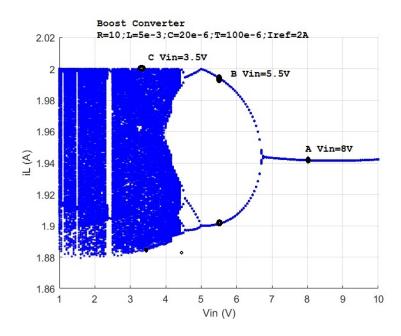

| 6.8  | Bifurcation diagram for $i_L$ with $V_{in}$ as a control parameter $(I_{ref}=2A)$      | 121 |

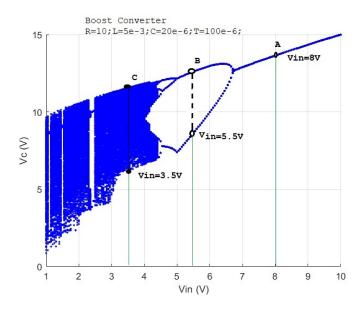

| 6.9  | Bifurcation diagram for $V_c$ with $V_{in}$ as a control parameter ( $I_{ref}=2A$ )    | 122 |

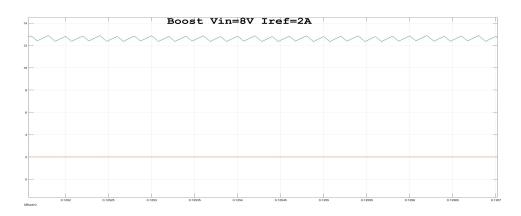

| 6.10 | Simulink output for the Output Voltage for $V_{in} = 8V$                               | 122 |

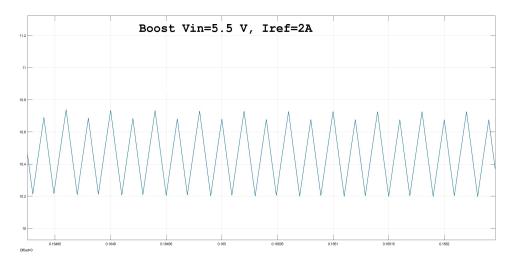

| 6.11 | Simulink output for the Output Voltage for $V_{in} = 5.5$ V                            | 122 |

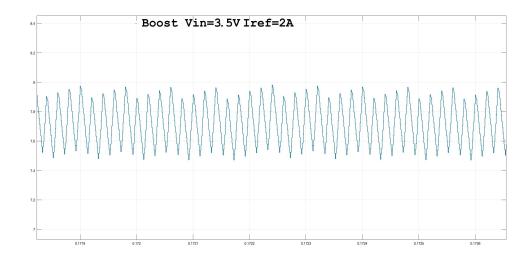

| 6.12 | Simulink output for the Output Voltage for $V_{in} = 3.5$ V                            | 123 |

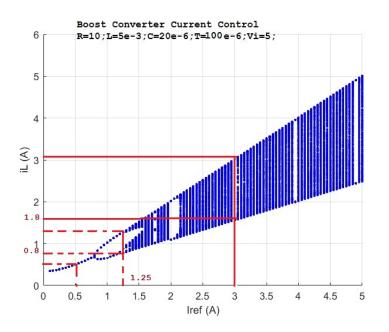

| 6.13 | Bifurcation diagram for $i_L$ with $I_{ref}$ as a control parameter ( $V_{in}=5V$ )    | 123 |

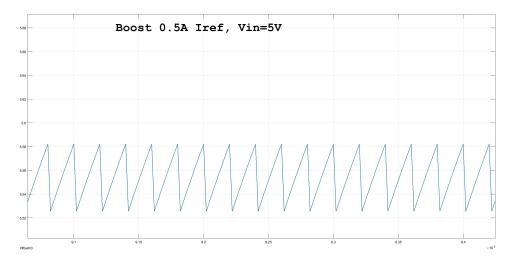

| 6.14 | Simulink output for the Output Voltage for $I_{ref} = 0.5 A$                           | 124 |

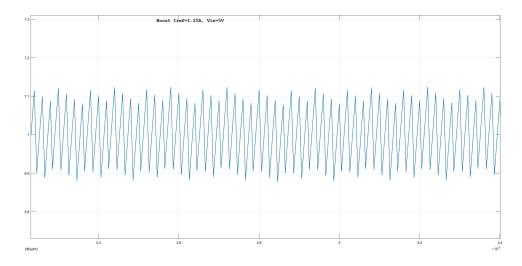

| 6.15 | Simulink output for the Output Voltage for $I_{ref} = 1.25 \text{A} \dots \dots \dots$ | 124 |

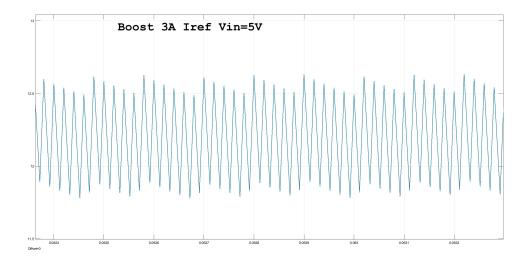

| 6.16 | Simulink output for the Output Voltage for $I_{ref} = 3A$                              | 125 |

## **Chapter 1**

# Introduction

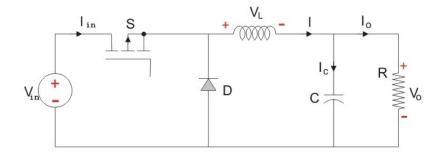

The demand and usage of modern electronic devices like cell phone, laptops, portable chargers and portable DVD players, solar cells etc. are increasing. These devices and their components need constant operating voltages and current. This is achieved by converters. AC-DC or DC-DC converters supply the necessary voltages by either stepping up or stepping down the levels. The constant output in the devices is taken care by a controller in the feedback path. DC-DC converters require to convert a fixed dc source into a variable dc source by either stepping up or stepping down the voltage. Switched-mode converters are DC-DC converters that supply dc loads with a regulated output voltage, and protection against over currents and short circuits.

The advantages of switched mode converters are

- 1. High Power Conversion efficiency.

- 2. Small size of passive components since they operate at high switching frequencies.

- 3. Reduced thermal losses.

DC-DC power converters find their use for personal computers, office equipment, spacecraft power systems, laptop computers, telecommunications equipment and dc motor drives and control circuits.

## **1.1 Types of DC-DC converters**

A switching converter is an electronic circuit that converts power using switching devices that are turned on and off at high frequencies, and storage components such as inductor or capacitor to supply power when the switching device is in its non-conduction state. DC-DC converters can be classified into two different types [1]- [5]

#### • DC-DC converters without isolation

These DC-DC converters do not have any isolation transformer between input and output stages. Some of the commonly used DC to DC converters without isolation are

- a. Buck converter

- b. Boost converter

- c. Buck-boost converter

The buck converter is step down converter (input voltage greater than the output voltage) whereas boost converter is a step up converter (input voltage less than the output voltage). The buck boost converter is derived from step up and step down converters. The buck boost converter can be operated in step up or step down mode based on duty cycle of switch. The step down and step up converters are basic converter topologies based on which other converters are derived.

#### • DC-DC converters with isolation

In this type of converter, a transformer is provided in between to isolate the input and output stages. The electrical isolation is an additional feature and is mainly useful in cases where the input voltage level (Vin) and output voltage level (Vout) differs significantly i.e. high or low values of Vout/Vin. The DC-DC converters with isolation is again divided into two types based on polarity of transformer core excitation

a) Unidirectional core excitation where core is excited with forward currents of only one direction. In these converters the isolation transformer core is operated in only the positive part of B-H curve.Some of the commonly used DC-DC converters with unidirectional core excitation are

- a. Fly back converter (derived from buck-boost converter)

- b. Forward converter (derived from buck converter)

- c. Full-bridge converter (derived from buck converter)

- d. Half-bridge converter (derived from buck converter)

- e. Push-pull converter (derived from buck converter)

b) Bidirectional core excitation where core is excited with currents in either direction. In these converters the isolation transformer core is operated alternatively in positive and negative portions of B-H curve. Some of the commonly used DC-DC converters with bidirectional core excitation are

- a. Flyback and forward converters.

- b. Push-pull, half-bridge and full-bridge converters.

- c. Resonant DC-DC converters.

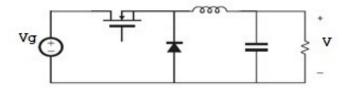

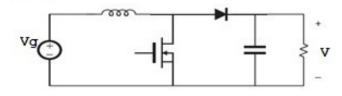

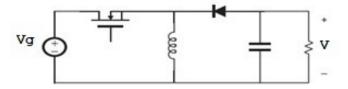

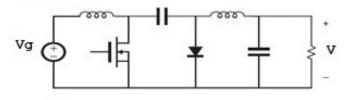

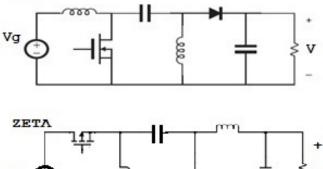

Figure 1.1 shows the basic types of converters used in switched mode supply. The cuk converter is a buck boost converter with a low ripple current. Single-ended primary-inductor converter (SEPIC) is a type of DC-DC converter that allows the output voltage to be greater than, less than, or equal to that at its input. Zeta converter is a fourth-order DC-DC converter made up of two inductors and two capacitors and capable of operating in either step-up or step-down mode. The converter system output is controlled by a controller whose main function is to operate the switching devices in a converter system and maintain a regulated output. The control technique plays a very important role in switched mode power converter. This research focuses on buck and boost converters. The converters are modeled, designed, constructed and analyzed for their closed loop performance.

#### **1.1.1 Performance Evaluation of Switching Converters**

The converters are tested for following power quality parameters

- 1. **Input Voltage Range:** The input voltage range determines the maximum and minimum allowable input supply for the converter. Input supplies higher than the maximum allowable input can damage the converter.

- 2. **Maximum Output Current:** It is the maximum output current that the converter can provide for the regulated voltage.

- 3. **DC Line Regulation:** DC line regulation is defined as the resulting change in the output voltage for a given change in the input voltage.

- 4. **DC Load Regulation:**The DC load regulation is the change in output voltage for a static change in output (load) current.

- 5. Efficiency: The efficiency is defined as the ratio of output power to input power. The efficiency depends on the internal losses of the converter.

#### Buck Converter

Boost Converter

Buck-boost Converter

Cuk Converter

SEPIC

Figure 1.1: Basic types of converter

#### 1.1.2 Necessity of Controller

The performance of a switching converter is dependent on the control strategy used. Controller plays an important role in regulating the output and achieving power quality of switching converters. The main component of a DC-DC converter is the controller. There are two types of control possible analog control and digital control. The digital control is widely used control over analog control. Advantages of digital control are as follows:

- 1. Digital controllers have immunity to noise.

- 2. They are less susceptible to component ageing and environmental variations.

- 3. They have improved sensitivity to parameter variation.

- 4. They have ease of integration with other digital systems.

- 5. Ability to implement sophisticated control schemes by means of programming.

- 6. They have low power consumption.

In DC-DC converters, the average output dc voltage needs to be controlled to a desired level. This control is achieved by controlling the on-off duration of the switches. Switched mode DC-DC converters utilize one or more switches to transform dc from one level to another. There are two methods to achieve it.

1) Constant frequency switching and adjusting the on time of the switch. Also called as pulse-width modulation(PWM) method,

2) Both switching frequency and on time of the switch are varied.

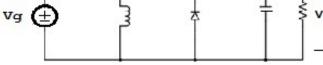

The PWM switching is widely used method as shown in figure 1.2. The control voltage is obtained by amplifying the error which is the difference between the actual output voltage and its desired reference value. The switch control signal is generated by comparing  $V_{control}$ with a repetitive waveform which is a saw tooth wave. The frequency is kept constant and is chosen to be in a few kilohertz to a few hundred kilohertz range. The average value of the output voltage depends on ton and toff. When the amplified error signal, which varies very slowly with time, is greater than the saw tooth waveform, the switch control becomes high, causing the switch to turn on. When the error signal is less than the saw tooth waveform, the switch turns off. The frequency of the repetitive waveform with a constant peak, establishes

Figure 1.2: Pulse Width Modulation

the switching frequency. In PWM method, a constant frequency is employed and the on time of the switch is adjusted to control the average output voltage. Thus, the switch duty Ratio D which is the ratio of the on duration to the switching time period is varied.

The other control method where in both on time and the switching frequency is varied has drawbacks of ripple components in the input and output waveform of the converter.

#### 1.1.3 Non linear Characteristics

Chaos is a kind of quasi-stochastic behaviors of determinate nonlinear system. DC–DC converters are typical nonlinear systems because of their switching processes. Some irregular behavior, such as sub harmonics and intermittent instability, has been observed in practice. The PWM switching is widely used method in DC-DC converters. Studies suggest that this type of switching leads to chaos. The method used to analyze chaos is bifurcation, which describe the changes in system behavior as a parameter is varied.

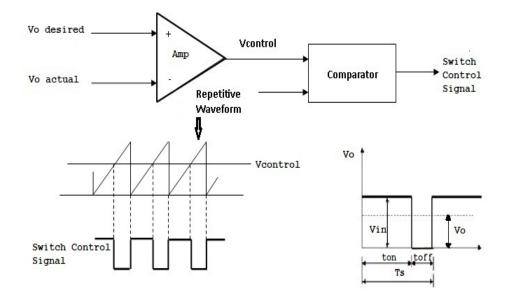

#### 1.1.4 VLSI Design Technology-FPGA Platform

Very large Scale Integration (VLSI) Design technology implements more than 10k transistors integrated on silicon chip(IC). It is one of the basic components of today's high technology. VLSI devices are found in all applications from simple household appliances to complex aircrafts. The advantages are smaller size, lower cost, lower power, higher reliability and

more functionality. VLSI family consists of Programmable Logic Devices (PLD's) and Application Specific Integrated Circuits (ASIC). The PLD's are further classified as

- 1. Field Programmable Gate Arrays (FPGAs)

- 2. Complex Programmable Logic Devices (CPLDs)

Figure 1.3: Programmable Logic devices

Figure 1.3 shows the structure of a FPGA and CPLD. FPGA's have logic blocks which are programmable. They can implement combinational as well as sequential logic. These blocks can be interconnected via a programmable interconnect. There is a periphery of programmable input output cells surrounding the core. CPLD has function blocks which implement the logic. They are connected by a switch matrix which is programmable. The function blocks and the the switch matrix are connected to the input output blocks. ASIC are specific IC's which can be produced in bulk once the PLD's are tested to satisfy the requirements. The prototype is designed on PLD which can be easily programmed using a bit file generated from the software.

### **1.2 Organization of the Report**

The organization of the report is as follows.

• Chapter 2 comprises of extensive research on the various types of control strategies for switching converters and different platforms for controller, VLSI based controllers and their various approaches to design and nonlinear control of converters wherein chaos

and the bifurcation theory are studied for DC-DC converters. It identifies the research gap and states the research objectives

- Chapter 3 discusses the buck converter, its working, modeling, frequency and time domain analysis for various types of controllers. Design and implementation of buck converter and testing FPGA based PI and PID controllers is discussed and performance is evaluated.

- Chapter 4 discusses the working, modeling and design for boost converter. The hardware is tested with the FPGA based controllers and performance is evaluated.

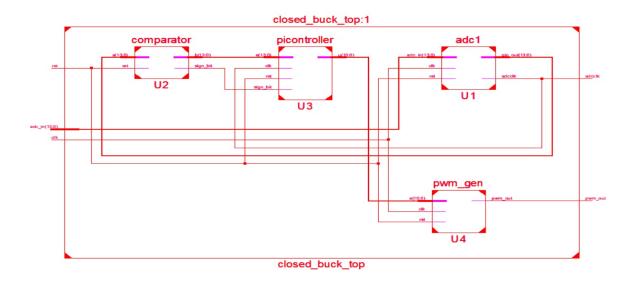

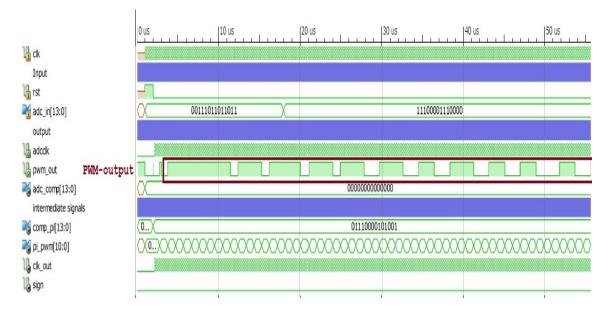

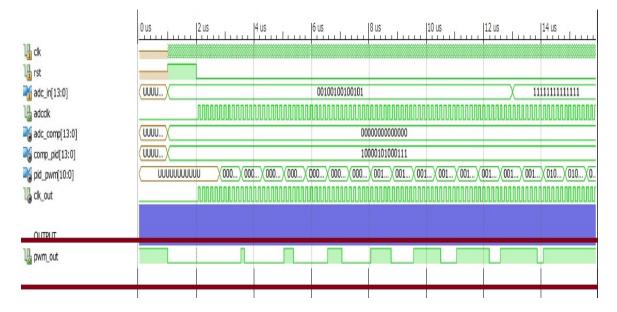

- Chapter 5 discusses the FPGA platform and the various methods of modeling. The closed loop is implemented on the FPGA using a FSM approach. The controller and the various blocks of control loop are designed, implemented and tested on a inbuilt logic analyzer. The device utilization for PI and PID controllers using Xilinx FPGA is obtained.

- Chapter 6 discusses nonlinearity in converters, chaos analysis for buck and boost converters. The iterative maps are derived and the simulations are performed to obtain bifurcations diagrams and phase portraits.

- Chapter 7 summarizes the research conclusions and discusses the future scope.

### **Chapter 2**

# **Literature Review**

A DC-DC converter is an electronic circuit or electromechanical device that converts a source of direct current from one voltage level to another. It is a type of electric power converter. Power levels range from very low (small batteries) to very high (high-voltage power transmission). A complete review of DC-DC converters, digital control methods, FPGA based control and applications, FPGA based discrete controllers and non linear analysis of converters is been placed.

## 2.1 Switching Converters

Converters employ switched mode devices and passive components like inductors and capacitors to regulate the output. The switched mode technology has reached a matured level for improving power quality in terms of power-factor correction (PFC), reduced total harmonic distortion at input ac mains and precisely regulated dc output in buck, boost, buck-boost and multilevel modes with unidirectional and bidirectional power flow as discussed in [5]. A complete survey of improved power quality converters is carried out by Bhim Singh et al [5] wherein different types of converter topologies, methods of control, design features, selection of components, suitability for certain applications are discussed. Various control techniques are used to get fast output response and high level of power quality at input ac mains and dc output. The control is implemented in three parts.

The important variables like the supply voltage, supply current, output voltage, inductor current, capacitor voltage are sensed and scaled to the required processor in the first stage. The sensing can be done by sensors. The scaling is done by CT or PT. Normally an ADC is required to convert the data for the controller.

- 2. The second stage is the actual controller with a control algorithm. These can be Analog controllers, low cost microcontroller, DSP or an ASIC. This depends on the rating, cost, customer requirements and the type of converter used. The control approach can be PI, PID, sliding mode, neural, fuzzy, adaptive control. Normally the output voltage of the converter is fed into these controllers to get the desired control.

- 3. The third stage is to derive the gating signals for the solid state devices. The controller output is compared with a reference signal to generate the required pulses. The design of this feedback is a important feature for fast response and improving the transient and steady state characteristics of the converter. The gating signals are fed through an optocoupler for isolation and then amplified to the desired value of the power devices.

Self Commutating Devices with high switching rates are used as switching devices. Mosfet's, IGBT, GTO are suitable for high switching rates with low, medium and high power ratings respectively. Many low cost, high volume dedicated IC's are available to control these converters. Measurement equipments like power analyzers, power scopes, power monitors, and spectrum analyzer are useful to find the factors like harmonic distortion, power factor, crest factor, ripples, and surges of the converter. Dedicated processors and ASIC's development for power converters are used because of low cost, ease in control, compact and high speed.

Switching converters are modeled using various methods like mathematical model, circuit, transfer function and state space approach. State space approach has advantages like compact representation of equations and ease of obtaining ac and dc transfer functions. Tan and Hoo [6] model and simulate the DC-DC converters in Matlab/Simulink using the state space block.

### 2.2 Digital Control methods

Yan-Fei Lin et al. [7] present an overview on advances in digital control. The converters considered are low to medium power AC-DC switching converters. The paper discusses the challenges to digital control. It also presents the research in online efficiency optimization, controller auto tuning and nonlinear control. Digital design techniques are reviewed. One of the basic technique is analog to digital design of the compensator. This is possible by either

backward Euler's method, Bilinear Transformation, Pole Zero Mismatches. But the drawbacks are discretization effects, delays associated with acquisition, computation and zero order hold. A small signal discrete model is analyzed. The delay time in the control loop can be related to the zero of the transfer function of control to output. The poles are unaffected. Also the equivalent series resistance (ESR) of the output capacitor does not add another zero. This zero is shifted opposite to the delay time. A direct digital method is discussed which can be useful in the implementation of a PID compensator. The computational delay in a multiplier can be reduced by a LUT or bit shifting. The current-programmed control presents a challenge to digital control. Methods of inductor current sampling have been discussed. The ideal is the mixed-signal controller which gives a faster response with added cost of control .The third part of the control strategy is the Digital Pulse Width Modulator(DPWM). The problem of Limit cycle oscillation (LCO) is associated with the quantization effects of the ADC and DPWM. High gain of the compensator integrator or very coarse quantizing step of the DPWM is the main reasons for LCO. Methods like tapped delay lines. Ring oscillators and hybrid DPWM techniques are reviewed. The PMBus interface has improved the power management communication and system level integration of controllers. Digital control is also used to adjust the parameters of the controller so that the efficiency is optimized. The switching losses in the converter can be reduced by control. Autotuning methods are reviewed. Digital control also helps in non linear and charge balance control which improves the dynamic response of the converter. Thus the advantages of Digital Control over analog control have been discussed.

K.N.Hasan et al. [8] describe a comparative study of current control methods of switch mode converters for photovoltaic applications. Average current control, hysteresis current control, current programmed control and nonlinear carrier control methods are discussed considering the input variations and load changes of a PV system. The current controllers are simulated in MATLAB/Simulink. A PV system is modeled and transient response and power quality issues like THD are compared for all the control strategies. The study concludes that all the current control methods can be implemented depending upon working conditions.

Hrishikesh Nene [9] presents a microcontroller based implementation of a controller for a DC-DC converter in automotive applications. There are two directions of power flow required—one high voltage bus to low voltage battery in the buck mode uses phase shifted full bridge(PSFB) with synchronous rectification and reverse mode is in the boost mode with a push pull stage. Peak current mode control of PSFB with adaptive zero voltage switching is implemented for buck converter and voltage control mode and average current control mode is implemented for boost converter. With the help of digital control, various control schemes are implemented on the same hardware. The modes of operation are defined for various controls. All operating modes are simulated and tested for a 600W system .The advantage of digital control is discussed.

Pallavee Bhatnagar et al. [10] present design of a DC-DC converter for a PV application using two control strategies. The converter is simulated for a switching frequency of 100 KHz using PWM control and hysteresis control. The PV array is simulated on SimScape software. The design of boost converter is explained. The output waveforms for voltage, current, inductor current, diode current are plotted for both types of controls. Both the controls are discussed with their advantages and disadvantages.

Souvik Chattopadhyay and Somshubhra Das [11] propose a digital current mode control technique for DC-DC converters. The inductor current is sampled only once in a switching instance. The slope of the ramp is determined analytically on the steady state conditions and hence there is less load of computation of the controller. The configuration of the DPWM for implementations of all the three variations of current-mode control, namely peak, average, and valley current-mode controls, has been proposed. The results are validated and implemented on TI's general purpose DSP starter kit.

Wang et al. [12] propose a controller for DC-DC switching converters used in battery powered hand held devices. Two modes digital pulse width modulator (DPWM) and an all digital pulse frequency modulator (DPFM) are discussed Advantages of DPWM are operation in high constant switching frequency whereas DPFM operates with low power consumption with control over switching frequency. An experimental FPGA prototype and an application specific IC (ASIC) are built for a low power buck converter and verified. The power is validated on 0.18um CMOS process. The DPWM architecture is modified from the conventional by an absence of external clock. A ring based segmented architecture is employed wherein the 2 blocks of 16 delay lines are connected to two multiplexers A and B. The logic is generated by the data lines selecting Mux A and Mux B. The hardware for DPWM is reduced with the ring oscillator. The DPFM architecture is race based with three blocks DPWM, End of Race (EOR) and DPFM.

Saggini et al. [13] describe an innovative method of designing a low-complexity, high-

performance digital controller based on different design strategy of current programmed control and variable frequency operation. The controller employs only two digital-to-analog converters (DACs) with low resolution, thus having a considerable resource saving. The control algorithm has been implemented into a commercially available FPGA device and tested on a prototype four-phase buck converter. The results are validated after experimentation.

A continuous time digital controller is designed by Zhenyu Zhao and Aleksandar Prodic [14] in which the sampled time is continuous and the amplitude is digitized. The application is a low-power, high frequency DC-DC switch-mode power supply. It controls both the transient and the steady state response. During transients it utilizes a fast voltage recovery mechanism based on the real time processing of output in digital domain. In steady state it is a conventional pulse width modulator. The processor consists of a set of asynchronous comparators, delay cells, and combinatorial logic. A capacitor charge balance algorithm is implemented which is based on the detection of the output voltage peak /valley point, thus eliminating the current measurement. It is experimented on an FPGA and tested with a low-power dc–dc converter operating at 400-kHz switching frequency. The fast recovery time is limited by the values of inductor and capacitor

A digital controller for an electric vehicle has been designed by Seung-mo Kim [15] which implements PI control and sliding mode control. It has Zero voltage switching and Phase shift full bridge topology. For voltage control PI is used and for protection from over current, over voltage sliding mode is used. It is implemented with a microcontroller and tested for a 13.7V, 130A Dc output.

S.Vijayalakshmi,K.Muthukumar [16] presents a sliding mode controller for DC-DC converters. The converter design is based on large signal model eliminating stability issues. A MATLAB/Simulink environment is used for design and simulation of closed loop synchronous buck converter in [17]. PID and auto tuned PID(AT PID) controller are designed and simulated. Transient response is analysed. The closed loop control simulation is helpful for FPGA or ASIC implementation,.

#### 2.3 FPGA based control

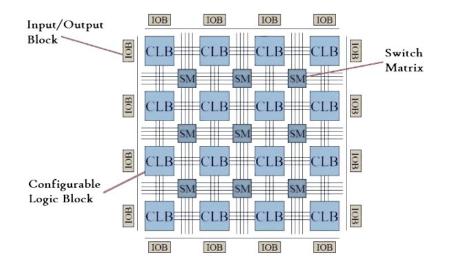

FPGA's are programmable logic devices. The technology used to program a FPGA is the with the SRAM memory. An FPGA is defined as a matrix of configurable logic blocks

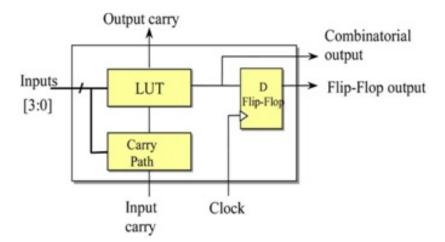

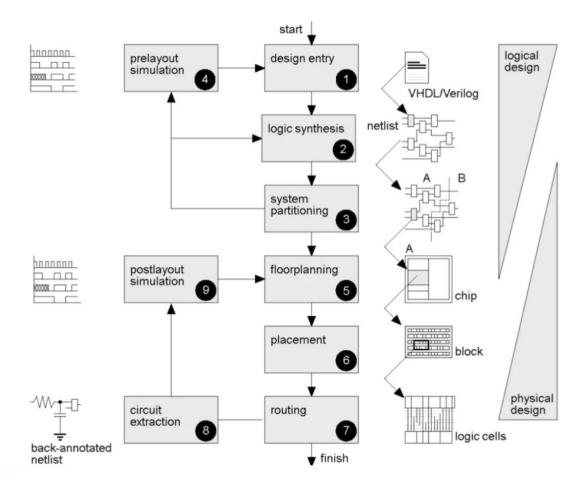

surrounded by a programmable interconnect structure. Programmable input output pins surround the core. FPGA based controllers implemented on a VLSI platform have high degree of parallelism and concurrency. E. Monmasson, L. Idkhajine and M. W. Naouar [18] discuss the FPGA platform for controllers design and its advantages. FPGAs are frequently used to implement complex functions due to recent advances in very large scale integration (VLSI). Design tools and methods are developed based on hardware description languages (HDLs) such as very high-speed integrated circuits (VHSICs) HDL (VHDL) and verilog. In addition IEEE standards are developed which aid in the development of these description languages in the field of microelectronics. Thus HDL can be designed at various levels of abstraction - system level, behavior level, RTL level and physical level. The main steps of FPGA based controllers are discussed in [18] which include the modular design, HDL coding, functional simulation, synthesis, physical design i.e partitioning, floor planning, routing and finally downloading on to FPGA chip. The design methodology can be implemented with different architectures using hardware description language(HDL) [18] or a Matlab Simulink environment with system generator tools [19]. A look up table(LUT) based and a multiplier based controller is designed on FPGA with area and power utilization as the constraints in [19].It gives a FPGA based PID controller for converter applications. The Proportional-Integral-Derivative (PID) controller is one of the most common types of feedback controllers that are used in dynamic systems. Matlab/Simulink environment is used for the PID controller design to generate a set of coefficients associated with the desired controller characteristics. These controller coefficients are then included in VHDL that implements the PID controller on to FPGA. Two architectures of PID controller are considered- multipliers and LUT based with their device utilization and power dissipation reports to show the resource utilization and power dissipation of selected FPGA. The architectures are implemented in FPGA Virtex-5(ML505) XC5VLX50T-1FF1136 (-1 speed grade) device Various papers have been reviewed with FPGA based control for DC-DC converters.

Miro Milanovic et al. [20] have designed a FPGA based PI controller for a DC-DC buck converter. An analog to digital converter, digital PI controller and PWM module are implemented on an FPGA. The controller design is carried out with various resources available on FPGA. A successive approximation based A/D converter is designed and implemented on FPGA. The comparator and integrator are external to the FPGA. The PI controller and the pulse width modulator are also implemented on FPGA. The output is a digital pulse which can be given to the switching device of the converter. The response of the controller is validated. It describes a possibility of digitized control for a buck converter.

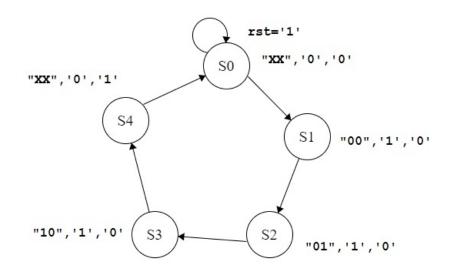

A PI controller is designed using a modular approach of datapaths and sequential paths in [21] which are controlled by a finite state machine. A comparison of a digital pulse-width modulator (DPWM) and a digital pulse-frequency modulator (DPFM) is performed in [22]. It implements the control loop on an ASIC 0.18um process with a controller operating in a DPWM operating at high frequency and DPFM featuring low power consumption. A complete programmable digital IC is designed and implemented for high switching frequencies in [23]. The said configuration has low silicon area, low power consumption and less complex logic as compared to an analog IC. Implementation has an ADC with delay line, LUT based digital compensator and a hybrid DPWM block. The VHDL design is tested on an ASIC of 0.5um technology. However, the design is implemented for high frequency of 1MHz. FPGA based control is implemented taking into consideration three main rules for design as described in [24]. They are simplification of the algorithm called refinement, using a modular approach for design and compatibility between the design and hardware. FPGA platform is used in [25] for testing and verifying different DC-DC converter topologies, control modes and switching frequencies, including a synchronized load change mechanism and a build-in acquisition memory and host interface for easy configuration,

A flexible experimental FPGA based platform for testing and verifying different DC-DC converter topologies, control modes and switching frequencies, including a synchronized load change mechanism and a built-in acquisition memory and host interface is presented in [25]. The controller is implemented on Xilinx Spartan 6 FPGA partly in pure logic and partly in a softcore microprocessor as a System-on-Chip solution (SoC). Each of the log-ical modules are implemented with low coupling between the modules for easy update of functionality.

Pulse width modulator is the basic block in the closed loop control. Two structures of high resolution digital pulse width modulator (DPWM) control circuit are discussed in [26]. Embedded digital clock manager (DCM) blocks and digital programmable delay circuits are employed as the basic resources to construct the field-programmable gate array (FPGA)-based DPWM implementations. The implementation is done on the Artix-7 FPGA device by Xilinx. For frequency of 200 MHz, the resolutions of the two structures are 625 ps and 500 ps, respectively.

Shettar et. al [27]proposes another digital PWM architecture for DC-DC Converters. This architecture includes a DCM block for improving the switching frequencies. Gray counter and one hot encoder circuit logic is implemented for low power consumption. With the counter bits zero, the enable logic is made high which turns on the one-hot encoder thus acting as the reset pin for it. Thus the one-hot encoder circuit is on only when required thus reducing the switching power. The MSB output of the one-hot encoder is given to the set pin of the RS flip-flop. Depending on the requirement of the duty cycle, the PWM control circuit resets the flip-flop thus producing a variable duty cycle. Xilinx 14.2 and ISim simulator is used for simulation.

#### 2.4 FPGA based discrete controllers

A digital PID controller is designed and simulated in Matlab using re-design approach in [28]. For a desired loop gain, crossover-frequency and phase-margin, digital filter direct form based PID controller is implemented. Mapping from analog to discrete domain is done by backward Euler method.

Different types of digital controllers, their design, tuning and frequency domain analysis is discussed in [29] [30] [31]. Compensator design for PI,PI with lead, lead, and PID is carried out in [32]- [37].

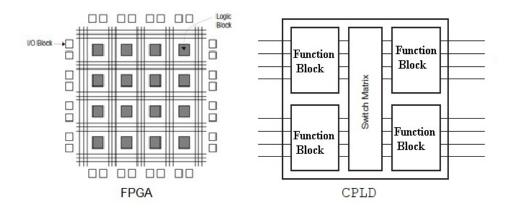

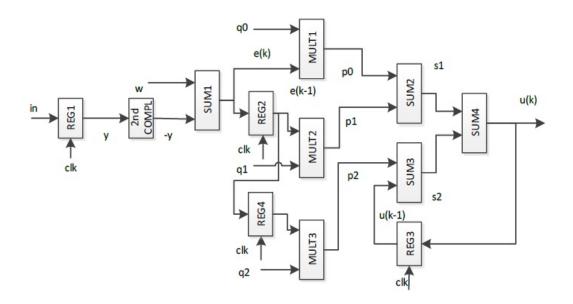

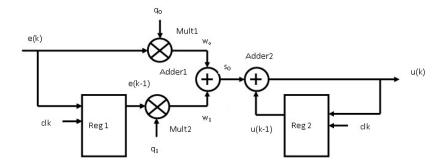

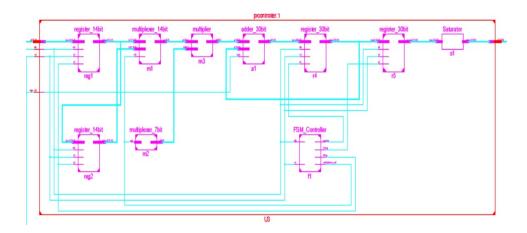

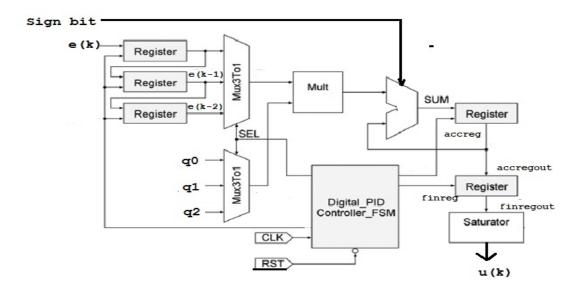

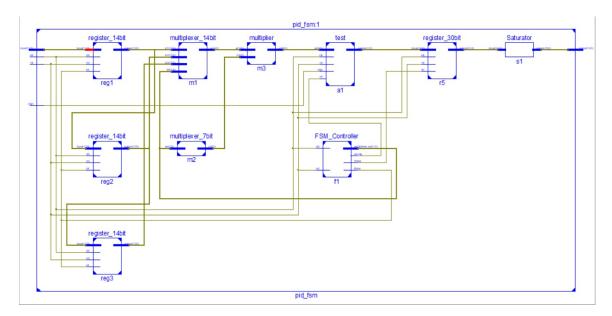

FPGA based PID controller hardware is shown in figure 2.1. It implements the discrete PID equation given by [38]

$$u[k] = u[k-1] + q_0 e(k) + q_1 e(k-1)$$

(2.1)

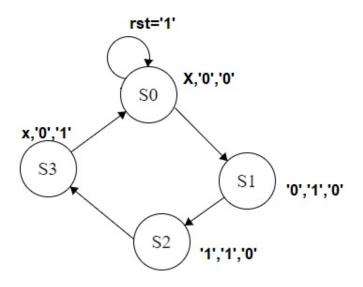

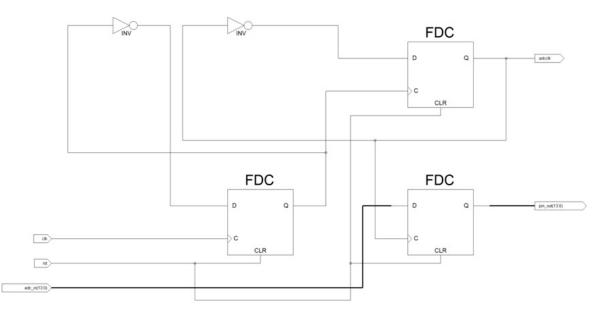

PID controller implementation on FPGA is also discussed in [39]. It utilizes three combinational logic multiplier, one subtractor three adders and three registers blocks. The method of ADC FPGA interfacing is discussed. Hardware software co-simulation model of PID controller using Matlab System Generator tools is implemented for a buck converter in [40] [41]. The hardware code is generated by the Matlab HDL coder which can be implemented on a FPGA. PID controller is implemented using the finite state machine (FSM) in [42]. This approach separates the data path and the sequential logic and is very useful for the PID controller. The controller triggers each state on a clock and thus the output is calculated.

FPGA software Vivado has its own simulation sub-systems making it possible to check the output. Three types of simulations are available- functional simulation, simulation after

Figure 2.1: Parallel architecture of Discrete PID for FPGA design [38]

synthesis and time simulation. A discrete PI controller is implemented in [43] using Xilinx Artix-7 FPGA. PID implementations on FPGA using floating point and fixed point representations are discussed in [44]. Shorter design cycles and resource savings is achieved in fixed point implementations. Thus discrete controllers on FPGA can be designed with behavior, parallel or FSM structure and are implemented with HDL coding or Matlab Simulink HDl coder.

## 2.5 Non Linear performance of switching converters

All power electronic circuits have the following properties:

- Switches make the circuit toggle between two or more different topologies, continuous conduction and discontinuous conduction with different sets of differential equations.

- Inductors and capacitors are the storage elements (inductors and capacitors) which absorb energy from a circuit, store it and return it.

- The switching times are nonlinear functions of the variables to be controlled (mostly the output voltage).

Thus, the feedback controlled switching is the basic source of non linearity in power electronic circuits. In addition there are nonlinearities present in the switches, storage elements

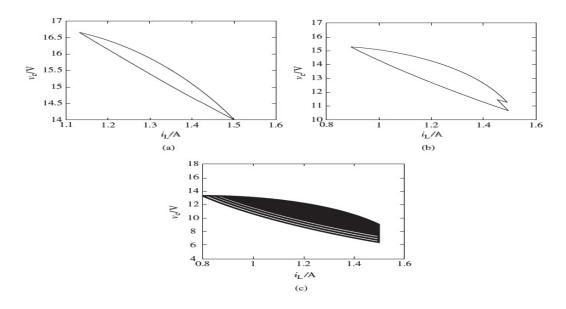

Figure 2.2: Phase portraits of (a) period-1, (b) period-2, and (c) chaos. [47]

and the electromagnetic couplings between components. However, the main source of nonlinearity is the switching element, which makes power electronic systems nonlinear even if all components are assumed to be ideal. [45]

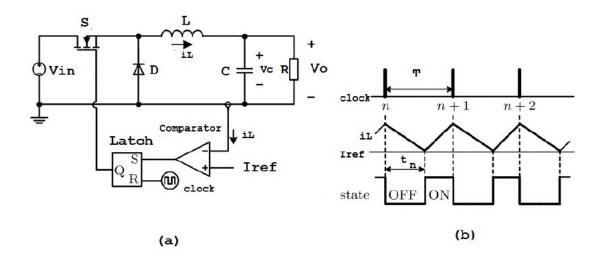

DC-DC converters exhibit bifurcation and chaos if switching action is governed by feedback control as observed in regulated power supplies. The cyclic switching operation and reactive components give rise to a variety of nonlinear behavior like bifurcation and chaos. Chaos in power electronics has been an area of intensive study for the last many years.Studies of the nonlinear behavior of power electronic converters began with DC–DC converters over the past 30 years. In 1984, the chaos phenomenon of the buck converter was first mentioned by Brochett and Wood. Hamill and Jefferies [46] introduced bifurcation and chaos in a PWM buck converter, where the difference equations and return maps were utilized to analyze its stability domain in 1988. The phenomena of boundedness, intermittency, and chaos were then observed in an experiment by Krein and Bass in 1990. [47]

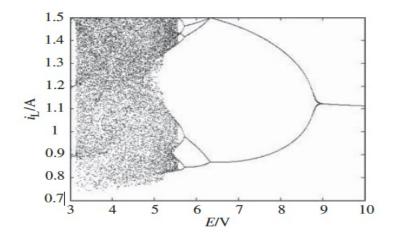

A phase portrait is a collection of trajectories that represents the solutions of equations in the state-space. Figure 2.2 gives the example of phase portraits for period-1, period-2 and chaos. A qualitative change in the number of solutions to a dynamical system by varying a parameter is called a bifurcation. A bifurcation diagram is a graphical representation of bifurcation [47]. A parameter is varied and plotted along the x-axis, and the asymptotic behavior of a sampled state variable is plotted on the y-axis as discrete points. A bifurcation diagram of a boost converter is shown in figure 2.3. If the system is operating in period-1

Figure 2.3: Bifurcation diagram of boost converter [47]

for some parameter values corresponding to a cycle in the phase portrait, there will be only one point in the bifurcation diagram. If it is in period-2, there will be two points. Such a bifurcation diagram summarizes the change in system behavior in response to the variation of a parameter.

Methods for controlling chaos in nonlinear systems can be classified into two general categories, namely, feedback control methods and non-feedback control methods. Feedback methods include the Ott-Grebogi-Yorke (OGY) method, Variable Ramp Compensation (VRC), Time-Delayed Feedback Control (TDFC) method. Examples of non-feedback methods include adaptive control, Resonant Parametric Perturbation (RPP). Based on the bifurcation analysis and parameter adjusting, the most simple chaotic control method is by changing the system parameters. G. Poddar, K. Chakrabarty, and S. Banerjee [48] propose two new methods for power electronic converters having a pulse width modulated (PWM)feedback controller.